# Chip Scale Package MMIC 50 GHz 10dB Attenuator ATN10-0050CSP1

#### 1 Device Overview

#### 1.1 General Description

The ATN10-0050CSP1 is a surface mount GaAs MMIC 10dB attenuator in a chip scale package (CSP). This attenuator is an ideal solution for attenuating a signal and can be used in a wide range of applications. The CSP allows for extreme miniaturization of SMT footprint while providing die-like performance. GaAs MMIC technology provides consistent unit-to-unit performance in a small, low-cost form factor. Compensates for high frequency board losses with a positive gain slope. A 50-ohm match is maintained over the entire operating frequency range.

QFN

#### 1.2 Features

- Small 1.5 x 1.5 mm package size

- 10dB attenuation from DC to 50 GHz

- 22dB typical return loss over operating band

- 1W Power Handling

- Low SWaP

- S2P data: <u>ATN10-0050CSP1.s2p</u>

# 1.3 Applications

- 5G

- Airborne Applications

- Test Equipment

- Amplitude Matching

- Precision Characterization

- High Channel Count Systems

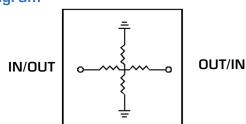

# 1.4 Functional Block Diagram

# 1.5 Part Ordering Options<sup>1</sup>

| Part<br>Number | Attenuation (dB) | Description                  | Package | Green<br>Status | Product<br>Lifecycle | Export<br>Classification |

|----------------|------------------|------------------------------|---------|-----------------|----------------------|--------------------------|

| ATN10-0050CSP1 | 10               | 1.5 x 1.5 mm<br>CSP          | CSP1    | RoHS            | Active               | EAR99                    |

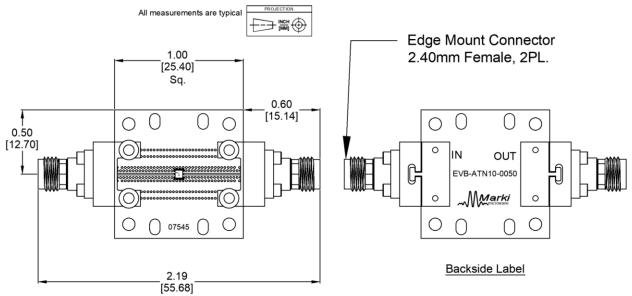

| EVB-ATN10-0050 | 10               | Connectorized<br>Eval Module | Module  |                 |                      |                          |

<sup>&</sup>lt;sup>1</sup> Refer to our <u>website</u> for a list of definitions for terminology presented in this table.

# **Table of Contents**

| 1 | Dev  | ice Overview                 | . 1 |

|---|------|------------------------------|-----|

|   | 1.1  | General Description          |     |

|   | 1.2  | Features                     | . 1 |

|   | 1.3  | Applications                 | . 1 |

|   | 1.4  | Functional Block Diagram     | . 1 |

|   | 1.5  | Part Ordering Options        | . 1 |

| 2 | Port | Configurations and Functions | . 3 |

|   | 2.1  | Port Diagram                 | . 3 |

|   | 2.2  | Port Functions               | . 3 |

| 3 | Spe  | cifications                  | 4   |

|   | 3.1  | Absolute Maximum Ratings     | 4   |

|   | 3.2 | Package    | Information4            | 4 |

|---|-----|------------|-------------------------|---|

|   | 3.3 | Electrica  | Specifications          | 4 |

|   | 3.4 | Typical P  | erformance Plots        | ō |

|   | 3.4 | 1 Elec     | trical Performance      | 5 |

|   | 3.4 | .2 Elec    | trical Performance Over |   |

|   | Tem | perature.  |                         | 5 |

| 4 | Med | chanical D | ata                     | 3 |

|   | 4.1 | CSP1 Pa    | ckage Outline Drawing ( | 3 |

|   | 4.2 | CSP1 Pa    | ckage Footprint (       | 3 |

|   | 4.3 | EVB Pac    | kage Outline Drawing    | 7 |

# **Revision History**

| Revision Code | Revision Date | Comment                   |  |

|---------------|---------------|---------------------------|--|

| -             | April 2022    | Datasheet Initial Release |  |

| А             | June 2022     | Outline Drawings Updated  |  |

# 2 Port Configurations and Functions

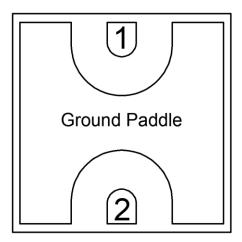

# 2.1 Port Diagram

An x-ray view of the ATN10-0050CSP1 package outline drawing is shown below. The ATN attenuators are symmetrical allowing Port 1 or Port 2 to be used as the input.

#### 2.2 Port Functions

| Port               | Function     | Description                                                            | Equivalent Circuit |  |

|--------------------|--------------|------------------------------------------------------------------------|--------------------|--|

| Pin 1              | Input/Output | Pin 1 and pin 2 are DC connected to each other and ground through a T- | Pin 1 Pin 2        |  |

| Pin 2 Input/Output |              | network of resistors.                                                  | <u></u>            |  |

| GND                | Ground       | SM package ground path is provided through the ground paddle.          | Pad⊶               |  |

# 3 Specifications

# 3.1 Absolute Maximum Ratings

The Absolute Maximum Ratings indicate limits beyond which damage may occur to the device. If these limits are exceeded, the device may be inoperable or have a reduced lifetime.

| Parameter                   | Maximum Rating | Units |

|-----------------------------|----------------|-------|

| Power Handling, at any Port | 1              | W     |

| Operating Temperature       | -55 to +100    | °C    |

| Storage Temperature         | -65 to +125    | °C    |

# 3.2 Package Information

| Parameter | Details                                              |     |

|-----------|------------------------------------------------------|-----|

| ESD       | Human Body Model (HBM), per MIL-STD-750, Method 1020 | TBD |

# 3.3 Electrical Specifications<sup>2</sup>

The electrical specifications apply at  $T_A=+25^{\circ}C$  in a  $50\Omega$  system. Typical data shown is for the equalizer in a SM package with a sine wave input applied to port 1.

Min and Max limits are guaranteed at  $T_A=+25^{\circ}C$ . All bare die are 100% DC tested and visually inspected.

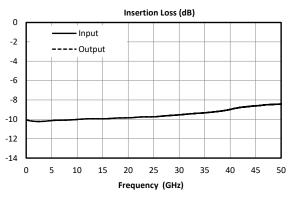

| Parameter           | Frequency Range<br>(GHz) | Min | Тур | Max |

|---------------------|--------------------------|-----|-----|-----|

| (10)                | DC to 30                 |     | 10  |     |

| Insertion Loss (dB) | 30 to 50                 |     | 9)  |     |

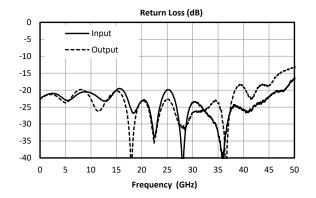

| Return Loss (dB)    | DC to 40                 | 15  | 24  |     |

| Hetuiti Loss (ub)   | 40 to 50                 |     | 18  |     |

| Impedance (Ω)       | DC to 50                 |     | 50  |     |

-

<sup>&</sup>lt;sup>2</sup> Attenuator is symmetrical. Reverse measurement is equivalent to forward measurement. All measurements taken in eval and de-embedded to the CSP1 pad interface.

# 3.4 Typical Performance Plots

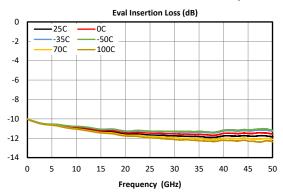

#### 3.4.1 Electrical Performance<sup>3</sup>

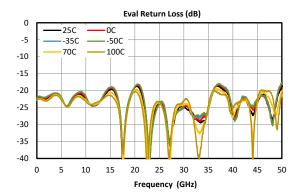

#### 3.4.2 Electrical Performance Over Temperature<sup>4</sup>

<sup>&</sup>lt;sup>3</sup> Electrical Performance Data is de-embedded to the CSP package ports

$<sup>^{\</sup>rm 4}$  Evaluation board performance is shown as a proxy for device performance due to fixturing variability over temperature

# **Mechanical Data**

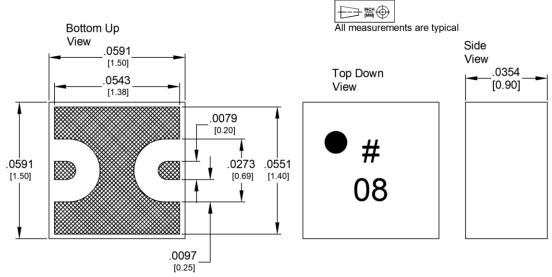

# 4.1 CSP1 Package Outline Drawing

Unless otherwise specified, dimensions are in inches. Tolerances are:

- 1. Front to back registration to be  $50.8\mu m$  max.

- 2. Circuits to be shipped individually.

- 3. Shaded areas are metalized.

- 4. Finish: Ni: 0.5 2.5 µm

Pd: 0.02 - 0.15 μm Au: 0.003 - 0.015 μm

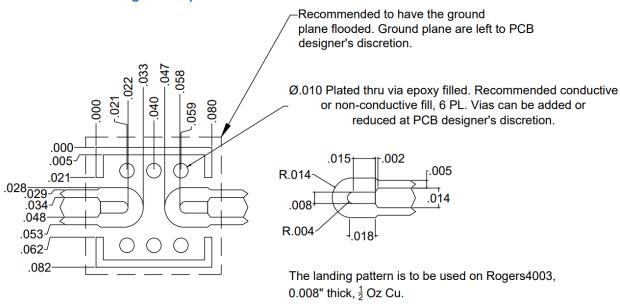

# 4.2 CSP1 Package Footprint

SM-Package Surface-Mount Landing Pattern

Click here for a DXF of the above layout.

Click here for leaded solder reflow. Click here for lead-free solder reflow

# 4.3 EVB Package Outline Drawing

Unless otherwise specified, dimensions are in inches. Tolerances are:

.XX ±.02 .XXX ±.005