## A87C257 256K (32K x 8) CHMOS LATCHED EPROM

Automotive

- Extended Automotive Temperature Range: -40°C to +125°C

- CHMOS/NMOS Microcontroller and Microprocessor Compatible

- 87C257-Integrated Address Latch

- Universal 28 Pin Memory Site, 2-line Control

- 120 ns Maximum Access Time

- **CMOS and TTL Compatible**

- **Low Power**

- 30 mA Max. Active

- 100 µA MAx. Standby

- **Fast Programming**

- Quick-Pulse Programming Algorithm

- Programming Time as Fast as 4 Seconds

- Noise Immunity Features

- ± 10% V<sub>CC</sub> Tolerance

- Maximum Latch-up Immunity

Through EPI Processing

- Available in 28-Pin Cerdip Package— Compact 32 Lead PLCC

(See Packaging Spec., Order #231369)

Intel's 87C257 CHMOS EPROM is a 256K-bit 5V only memory organized as 32,768 8-bit words. It employs advanced CHMOS\*III-E circuitry for systems requiring low power, high speed performance, and noise immunity. The 87C257 is optimized for compatibility with multiplexed address/data bus microcontrollers such as Intel's 16 MHz 80C51, 80C152, 80C252, and 8 MHz 80C196.

The 87C257 incorporates latches on all address inputs to minimize chip count, reduce cost, and simplify design of multiplexed bus systems. The 87C257's internal address latch allows address and data pins to be tied directly to the processor's multiplexed address/data pins. Address information (inputs  $A_0-A_{14}$ ) is latched early in the memory-fetch cycle by the falling edge of the ALE input. Subsequent address information is ignored while ALE remains low. The EPROM can then pass data (from pins  $O_0-O_7$ ) on the same bus during the last part of the memory-fetch cycle.

The 87C257 is offered in a ceramic DIP and PLCC packages, providing flexibility in prototyping and R&D environments. The 87C257 employs the Quick-Pulse Programming™ Algorithm for fast and reliable programming.

Intel's EPI processing achieves the highest degree of latch-up protection. Address and data pin latch-up prevention is provided for stresses up to 100 mA from -1V to  $V_{\rm CC}$  + 1V.

In order to meet the rigorous environmental requirements of automotive applications, Intel offers the 87C257 in extended Automotive temperature range. Operational characteristics are guaranteed over the range of -40°C to +125°C ambient.

\*HMOS and CHMOS are patented processes of Intel Corporation.

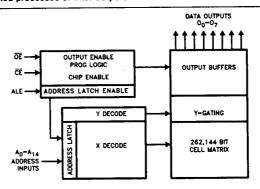

Figure 1. Block Diagram

August 1992 Order Number: 290142-004

290142-1

| - |    |   |   |   |    |  |

|---|----|---|---|---|----|--|

| D | in | м | 2 | m | Δe |  |

|   |    |   |   |   |    |  |

| A <sub>0</sub> -A <sub>14</sub> | ADDRESSES                               |

|---------------------------------|-----------------------------------------|

| 00-07                           | OUTPUTS                                 |

| ŌĒ                              | OUTPUT ENABLE                           |

| CE                              | CHIP ENABLE                             |

| ALE/V <sub>PP</sub>             | Address Latch<br>Enable/V <sub>PP</sub> |

| N.C.                            | NO CONNECT                              |

| D.U.                            | DON'T USE                               |

|   | 87C64           |

|---|-----------------|

| i | V <sub>PP</sub> |

|   | A <sub>12</sub> |

|   | A <sub>7</sub>  |

|   | A <sub>6</sub>  |

|   | A <sub>5</sub>  |

| ĺ | A <sub>4</sub>  |

|   | A <sub>3</sub>  |

|   | A <sub>2</sub>  |

| 1 | $A_1$           |

|   | A <sub>0</sub>  |

|   | $O_0$           |

| I | 01              |

|   | 02              |

|   | Gnd             |

| 87C64                            |   |

|----------------------------------|---|

| V <sub>CC</sub><br>PGM           |   |

| N.C                              | ı |

| A <sub>8</sub>                   |   |

| A <sub>9</sub>                   | I |

| A11                              | l |

| ŌĒ                               | I |

| A <sub>10</sub>                  |   |

| ALE/CE                           | ı |

| 07                               |   |

| O <sub>6</sub><br>O <sub>5</sub> | ı |

| O <sub>5</sub>                   | ۱ |

| O <sub>3</sub>                   | I |

| <b>U</b> 3                       | 1 |

290142-11

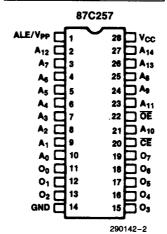

Figure 2. DIP Pin Configuration

#### NOTE:

Intel "Universal Site"-Compatible EPROM Pin Configurations are Shown in the Blocks Adjacent.

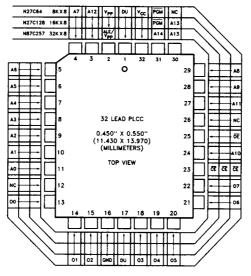

Figure 3. PLCC Lead Configuration

#### NOTE:

Intel "Universal Site"-Compatible EPROM Pin Configurations are Shown in the Blocks Adjacent.

# AUTOMOTIVE TEMPERATURE EPROMS

Intel automotive EPROMs have received additional processing to enhance product characteristics. The automotive temperature range is  $-40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  during operating modes.

### **AUTOMOTIVE OPTIONS**

#### Versions

| Speed    | Packaging Options |      |  |  |  |

|----------|-------------------|------|--|--|--|

| Versions | Cerdip            | PLCC |  |  |  |

| -120V10  | AD                | AN   |  |  |  |

| -200V10  | AD                | AN   |  |  |  |

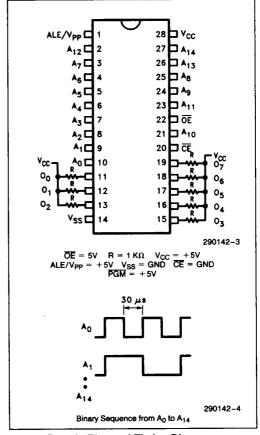

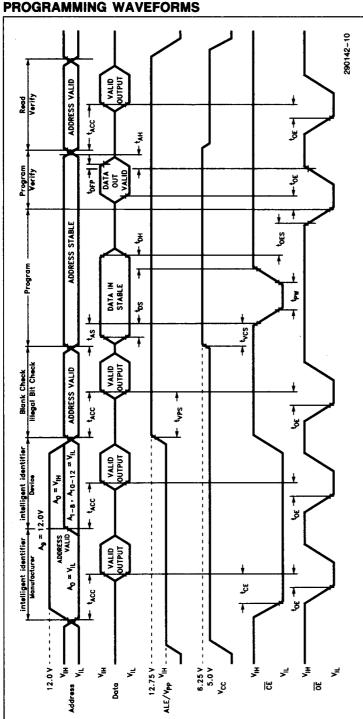

**Burn-In Bias and Timing Diagrams**

#### **ABSOLUTE MAXIMUM RATINGS\***

| ) |

|---|

| ) |

| ) |

| ) |

| ) |

| ) |

| ) |

|   |

| Maximum Junction Temperature (TJ) 140  | ٥°C |

|----------------------------------------|-----|

| Maximum Thermal Resistance             |     |

| Junction to Ambient ( $\theta_{JA}$ ): |     |

| Cerdip                                 | /W  |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### **READ OPERATION**

## **DC CHARACTERISTICS** TTL and NMOS inputs $-40^{\circ}$ C $\leq T_{A} \leq +125^{\circ}$ C

| Symbol           | Parameter                        |           | Notes | Min  | Typ(2) | Max                   | Units | Test Condition                                                                     |

|------------------|----------------------------------|-----------|-------|------|--------|-----------------------|-------|------------------------------------------------------------------------------------|

| ILI              | Input Load Current               |           |       |      | 0.01   | ± 1.0                 | μΑ    | V <sub>IN</sub> = 0V, 5.5V                                                         |

| lo               | Output Leakage Current           |           |       |      | 0.01   | ±10                   | μΑ    | V <sub>OUT</sub> = 0V, 5.5V                                                        |

| ISB              | V <sub>CC</sub> Current Standby  | Switching |       |      |        | 10                    | mA    | CE = ALE = VIH                                                                     |

|                  | with Inputs—                     | Stable    |       |      |        | 1.0                   | mA    | CE = VIH, ALE = VIL                                                                |

| I <sub>CC1</sub> | V <sub>CC</sub> Current Active   |           | 4     |      |        | 30                    | mA    | CE = V <sub>IL</sub> , ALE = V <sub>IH</sub><br>f = 5 MHz, I <sub>OUT</sub> = 0 mA |

| VIL              | Input Low Voltage (±10%          | Supply)   | 1     | -0.5 |        | 0.8                   | V     |                                                                                    |

| V <sub>IH</sub>  | Input High Voltage (±10% Supply) |           |       | 2.0  |        | V <sub>CC</sub> + 0.5 | ٧     |                                                                                    |

| VOL              | Output Low Voltage               |           |       |      |        | 0.45                  | ٧     | I <sub>OL</sub> = 2.1 mA                                                           |

| V <sub>OH</sub>  | Output High Voltage              |           |       | 2.4  |        |                       | ٧     | $I_{OH} = -400  \mu A$                                                             |

| los              | Output Short Circuit Currer      | nt        | 5     |      |        | 100                   | mA    |                                                                                    |

## DC CHARACTERISTICS CMOS Inputs $-40^{\circ}C \le T_A \le +125^{\circ}C$

| Symbol           | Paramete                        | r           | Notes | Min                   | Typ(2) | Max                   | Units | Test Condition                                                                     |

|------------------|---------------------------------|-------------|-------|-----------------------|--------|-----------------------|-------|------------------------------------------------------------------------------------|

| ارر              | Input Load Current              |             |       |                       | 0.01   | ± 1.0                 | μΑ    | V <sub>IN</sub> = 5.5V                                                             |

| ILO              | Output Leakage Curre            | nt          |       |                       | 0.01   | ± 10.0                | μΑ    | V <sub>OUT</sub> = 05, 5.5V                                                        |

| ISB              | V <sub>CC</sub> Current Standby | Switching   | 3     |                       |        | 6                     | mA    | CE = ALE = VIH                                                                     |

|                  | with Inputs— Stable             |             |       |                       |        | 100                   | μA    | CE = VIH, ALE = VIL                                                                |

| Icc <sub>1</sub> | V <sub>CC</sub> Current Active  |             | 4     |                       |        | 15                    | mA    | CE = V <sub>IL</sub> , ALE = V <sub>IH</sub><br>f = 5 MHz, I <sub>OUT</sub> = 0 mA |

| VIL              | Input Low Voltage (±1           | 10% Supply) |       | -0.2                  |        | 0.8                   | ٧     |                                                                                    |

| V <sub>IH</sub>  | Input High Voltage (±           | 10% Supply) |       | 0.7 V <sub>CC</sub>   |        | V <sub>CC</sub> + 0.2 | ٧     |                                                                                    |

| V <sub>OL</sub>  | Output Low Voltage              |             |       |                       |        | 0.4                   | ٧     | I <sub>OL</sub> = 2.1 mA                                                           |

| V <sub>OH</sub>  | Output High Voltage             |             |       | V <sub>CC</sub> - 0.8 |        |                       | ٧     | I <sub>OH</sub> = -2.5 mA                                                          |

| los              | Output Short Circuit Co         | urrent      | 5     |                       |        | 100                   | mA    |                                                                                    |

#### NOTES

- 1. Minimum DC input voltage is -0.5V. During transitions, the inputs may undershoot to -2.0V for periods less than 20 ns. Maximum DC voltage on output pins is  $V_{CC} + 0.5$ V which may overshoot to  $V_{CC} + 2$ V for periods less than 20 ns. 2. Typical limits are at  $V_{CC} = 5$ V,  $T_A = +25$ °C.

- 3.  $\overrightarrow{CE}$  is  $V_{CC} \pm 0.2V$ . All other inputs can have any value within spec.

- 4. Maximum current value is with outputs O<sub>0</sub> to O<sub>7</sub> unloaded.

- 5. Output shorted for no more than one second. No more than one output shorted at a time. IOS is sampled but not 100% tested.

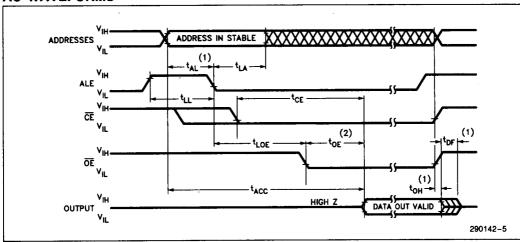

#### **READ OPERATION**

## AC CHARACTERISTICS(1) $-40^{\circ}$ C $\leq T_A \leq +125^{\circ}$ C

| Versions            |                     | V <sub>CC</sub> ± 10% | 87C257 | -120V10 | 87C257 | Units |       |

|---------------------|---------------------|-----------------------|--------|---------|--------|-------|-------|

| Symbol              | Characte            | eristic               | Min    | Max     | Min    | Max   | Units |

| tACC                | Address to Output D | elay                  |        | 120     |        | 200   | ns    |

| t <sub>CE</sub>     | CE to Output Delay  |                       |        | 120     |        | 200   | ns    |

| t <sub>OE</sub>     | OE to Output Delay  |                       |        | 55      |        | 75    | ns    |

| t <sub>DF</sub> (2) | OE High to Output H | ligh Z                | -      | 30      |        | 40    | ns    |

| t <sub>OH</sub> (2) | Output Hold from Ac |                       | 0      |         | 0      |       | ns    |

| t <sub>LL</sub>     | Latch Deselect Widt | h                     | 50     |         | 50     |       | ns    |

| t <sub>AL</sub> (2) | Address to Latch Se | it-Up                 | 15     |         | 15     |       | ns    |

| t <sub>LA</sub>     | Address Hold from I | ATCH                  | 30     |         | 30     |       | ns    |

| tLOE                | ALE to Output Enab  | le                    | 30     |         | 30     |       | ns    |

#### **NOTES:**

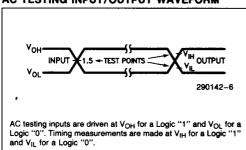

See AC Testing Input/Output Waveforms for timing measurements.

2. Guaranteed and sampled.

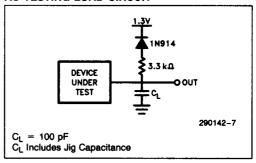

#### **AC CONDITIONS OF TEST**

| Input Rise and Fall Times (10% to 90° | %) 10 ns                                   |

|---------------------------------------|--------------------------------------------|

| Input Pulse Levels                    | $\dots$ V <sub>OL</sub> to V <sub>OH</sub> |

| Input Timing Reference Level          | 1.5V                                       |

| Output Timing Reference Level         | Vii and Viii                               |

#### **AC WAVEFORMS**

#### NOTES:

1. This parameter is only sampled and is not 100% tested.

2. OE may be delayed up to t<sub>CE</sub>-t<sub>OE</sub> after the falling edge of CE without impact on t<sub>CE</sub>.

CAPACITANCE(1) TA = 25°C, f = 1.0 MHz

| Symbol | Parameter                   |    | Units | Conditions            |

|--------|-----------------------------|----|-------|-----------------------|

| CiN    | Address/Control Capacitance | 6  | pF    | V <sub>IN</sub> = 0V  |

| Cout   | Output Capacitance          | 12 | рF    | V <sub>OUT</sub> = 0V |

#### NOTE:

1. Sampled. Not 100% tested.

#### AC TESTING INPUT/OUTPUT WAVEFORM

#### **AC TESTING LOAD CIRCUIT**

#### **DEVICE OPERATION**

Table 1 lists 87C257 operating modes. Read mode requires a single 5V power supply. All input levels are TTL or CMOS except Ag in Intelligent Identifier mode and Vpp.

**Table 1. Mode Selection**

| Pins                                                | CE              | ŌĒ              | Ag                 | A <sub>0</sub>  | ALE/<br>V <sub>PP</sub>     | Vcc             | Outputs          |

|-----------------------------------------------------|-----------------|-----------------|--------------------|-----------------|-----------------------------|-----------------|------------------|

| Mode                                                |                 |                 |                    |                 |                             |                 |                  |

| Read                                                | V <sub>IL</sub> | VIL             | χ(1)               | ×               | х                           | 5.0V            | D <sub>OUT</sub> |

| Output Disable                                      | V <sub>IL</sub> | V <sub>IH</sub> | Х                  | Х               | Х                           | 5.0V            | High Z           |

| Standby                                             | V <sub>IH</sub> | Х               | Х                  | X               | Х                           | 5.0V            | High Z           |

| Programming                                         | V <sub>IL</sub> | V <sub>IH</sub> | Х                  | х               | (Note 4)                    | (Note 4)        | D <sub>IN</sub>  |

| Program Verify                                      | V <sub>IH</sub> | VIL             | X                  | X               | (Note 4)                    | (Note 4)        | D <sub>OUT</sub> |

| Optional Program<br>Verify                          | V <sub>IL</sub> | V <sub>IL</sub> | x                  | x               | V <sub>CC</sub><br>(Note 4) | (Note 4)        | D <sub>OUT</sub> |

| Program Inhibit                                     | V <sub>IH</sub> | V <sub>IH</sub> | X                  | X               | (Note 4)                    | (Note 4)        | High Z           |

| Intelligent Identifier <sup>(3)</sup> -Manufacturer | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>H</sub> (2) | VIL             | X                           | V <sub>CC</sub> | 89 H             |

| Intelligent Identifier <sup>(3)</sup> -87C257       | VIL             | V <sub>IL</sub> | V <sub>H</sub> (2) | V <sub>IH</sub> | х                           | V <sub>CC</sub> | 24 H             |

#### NOTES:

- 1. X can be  $V_{IL}$  or  $V_{IH}$ . 2.  $V_{H}$  = 12.0V ±0.5V.

- 3.  $A_1-A_8$ ,  $A_{10-12}=V_{IL}$ ,  $A_{13-14}=X$ . 4. See Table 2 for  $V_{CC}$  and  $V_{PP}$  programming voltages.

The 87C257 has two control functions; both must be logically active to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and the device-select. Output enable ( $\overline{\text{OE}}$ ) gates data to the output pins by controlling the output buffer. When the address is stable (ALE = V<sub>IH</sub>) or latched (ALE = V<sub>IL</sub>), the address access time (t<sub>ACC</sub>) equals the delay from  $\overline{\text{CE}}$  to output (t<sub>CE</sub>). Outputs display valid data t<sub>OE</sub> after the falling edge of  $\overline{\text{OE}}$ , assuming t<sub>ACC</sub> and t<sub>CE</sub> times are met.

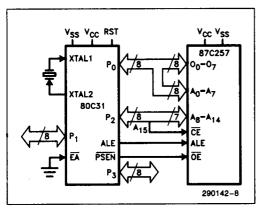

The 87C257 reduces the hardware interface in multiplexed address-data bus systems. Figure 4 shows a low power, small board space, minimal chip 87C257/microcontroller design. The processor's multiplexed bus (AD<sub>0-7</sub>) is tied to the 87C257's address and data pins. No separate address latch is needed because the 87C257 latches all address inputs when ALE is low.

The ALE input controls the 87C257's internal address latch. As ALE transitions from  $V_{IH}$  to  $V_{IL}$ , the last address present at the address pins is retained. The  $\overline{OE}$  control can then enable EPROM data onto the bus.

Figure 4. 80C31 with 87C257 System Configuration

## Standby Mode

The standby mode substantially reduces  $V_{CC}$  current. When  $CE = V_{IH}$ , the standby mode places the outputs in a high impedance state, independent of the OE input.

#### **Two Line Output Control**

EPROMs are often used in larger memory arrays. Intel provides two contol inputs to accommodate multiple memory connections. Two-line control provides for:

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To efficiently use these two control inputs, an address decoder should enable  $\overline{CE}$ , while  $\overline{OE}$  should be connected to all memory-array devices and the system's  $\overline{READ}$  control line. This assures that only selected memory devices have active outputs while deselected memory devices are in low-power standby mode.

#### SYSTEM CONSIDERATIONS

EPROM power switching characteristics require careful device decoupling. System designers are interested in three supply current (ICC) issues-standby current levels, active current levels, and transient current peaks produced by falling and rising edges of Chip Enable. Transient current magnitudes depend on the device outputs' capacitive and inductive loading. Two-Line Control and proper decoupling capacitor selection will suppress transient voltage peaks. Each device should have a 0.1 µF ceramic capacitor connected between its V<sub>CC</sub> and GND. This high frequency, low inherent-inductance capacitor should be placed as close as possible to the device. Additionally, for every eight devices, a 4.7 µF electrolytic capacitor should be placed between V<sub>CC</sub> and GND at the array's power supply connection. The bulk capacitor will overcome voltage slumps caused by PC board trace inductances.

#### PROGRAMMING MODES

Caution: Exceeding 14V on V<sub>PP</sub> will permanently damage the device.

Initially, and after each erasure, all EPROM bits are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" are programmed, the data word

can contain both "1s" and "0s". Ultraviolet light erasure is the only way to change "0s" to "1s".

The programming mode is entered when  $V_{PP}$  is raised to its programming voltage (see Table 2). Data is programmed by applying an 8-bit word to the output pins  $(O_{0-7})$ . Pulsing  $\overline{CE}$  to TTL-low while  $\overline{CE} = V_{IH}$  will program data. TTL levels are required for address and data inputs.

### **Program Inhibit**

The Program Inhibit mode allows parallel programming of multiple EPROMs with different data. With V<sub>PP</sub> at its programming voltage, a  $\overline{CE}$ -low pulse programs the desired EPROM.  $\overline{CE}$ -high inputs inhibit programming of non-targeted devices. Except for  $\overline{CE}$  and  $\overline{OE}$ , parallel EPROMs may have common inputs.

### **Program Verify**

With V<sub>PP</sub> and V<sub>CC</sub> at their programming voltages, a verify (read) determines that bits are correctly programmed. The verify is performed with  $\overline{CE} = V_{IH}$  and  $\overline{OE} = V_{IL}$ . Valid data is available t<sub>OE</sub> after  $\overline{OE}$  falls low.

### Intelligent Identifier Mode

The Intelligent Identifier Mode will determine an EPROM's manufacturer and device type. Programming equipment can automatically match a device with its proper programming algorithm.

This mode is activated when programming equipment forces 12V  $\pm 0.5$ V on the EPROM's  $A_9$  address line. With  $A_1$ – $A_8$ ,  $A_{10}$ – $A_{12}$  =  $V_{IL}$  ( $A_{13}$ –14 are don't care), address line  $A_0$  =  $V_{IL}$  will present the manufacturer's code and  $A_0$  =  $V_{IH}$  the device code (see Table 1). When  $A_9$  =  $V_{H}$ , ALE need not be toggled to latch each identifier address. This mode

functions in the 25°C ±5°C ambient temperature range required during programming.

# ERASURE CHARACTERISTICS (FOR CERDIP EPROMS)

Exposure to light of wavelength shorter than 4000 Angstroms (Å) begins EPROM erasure. Sunlight and some fluorescent lamps have wavelengths in the 3000–4000Å range. Constant exposure to room-level fluorescent light can erase an EPROM in about 3 years (about 1 week for direct sunlight). Opaque labels over the window will prevent unintentional erasure under these lighting conditions.

The recommended erasure procedure is exposure to 2537Å ultraviolet light. The minimum integrated dose (intensity x exposure time) is 15 Wsec/cm². Erasure time using a 12000  $\mu$ W/cm² ultraviolet lamp is approximately 15 to 20 minutes. The EPROM should be placed about 1 inch from the lamp. The maximum integrated dose is 7258 Wsec/cm² (1 week @ 12000  $\mu$ W/cm²). High intensity UV light exposure for longer periods can cause permanent damage.

#### **CHMOS NOISE CHARACTERISTICS**

System reliability is enhanced by Intel's CHMOS EPI-process techniques. Protection on each data and address pin prevents latch-up; even with 100 mA currents and voltages from  $-1\mbox{V}$  to  $\mbox{V}_{CC}$  + 1V. Additionally, the  $\mbox{V}_{PP}$  pin is designed to resist latch-up to the 14V maximum device limit.

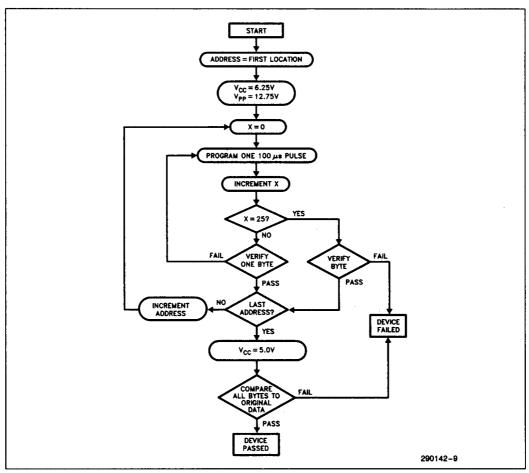

Figure 5. Quick-Pulse Programming Algorithm

## **Quick-Pulse Programming Algorithm**

The Quick-Pulse Programming algorithm programs Intel's 87C257 EPROM. Developed to substantially reduce production programming throughput time, this algorithm can program a 87C257 in under four seconds. Actual programming time depends on the PROM programmer used.

The Quick-Pulse Programming algorithm uses a 100 microsecond initial-pulse followed by a byte verification to determine when the addressed byte is correctly programmed. The algorithm terminates if 25 100 µs pulses fail to program a byte. Figure 5 shows the Quick-Pulse Programming algorithm flowchart.

The entire program-pulse/byte-verify sequence is performed with  $V_{CC}=6.25V$  and  $V_{PP}=12.75V$ . When programming is complete, all bytes should be compared to the original data with  $V_{CC}=5.0V$ .

## **Alternate Programming**

Intel's 27C256 Quick-Pulse Programming algorithms will also program the 87C257. By overriding a check for the Intelligent Identifier, older or non-upgraded PROM programmers can program the 87C257. See Intel's 27C256 data sheets for programming waveforms of these alternate algorithms.

In addition to the Quick-Pulse Programming Algorithm, the 87C257 has also been characterized for the Quick-Board Programming Algorithm. The Quick-Board Programming Algorithm was developed for specific automotive applications using Intel's 1.0 micron EPROM products. Contact the factory or an automotive sale representative for any information regarding the Quick-Board Programming Algorithm.

## DC PROGRAMMING CHARACTERISTICS TA = 25°C ±5°C

Table 2

| Symbol                         | Parameter                                     |                       | Test Conditions       |      |                                      |

|--------------------------------|-----------------------------------------------|-----------------------|-----------------------|------|--------------------------------------|

|                                | rai ailletei                                  | Min                   | Max                   | Unit |                                      |

|                                | Input Current (All Inputs)                    |                       | 1.0                   | μА   | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

| V <sub>IL</sub>                | Input Low Level (All Inputs)                  | -0.2                  | 0.8                   | ٧    |                                      |

| V <sub>IH</sub>                | Input High Level                              | 2.0                   | V <sub>CC</sub> + 0.5 | ٧    |                                      |

| V <sub>OL</sub>                | Output Low Voltage During Verify              |                       | 0.4                   | ٧    | I <sub>OL</sub> = 2.1 mA             |

| V <sub>OH</sub>                | Output High Voltage During Verify             | V <sub>CC</sub> - 0.8 |                       | ٧    | $I_{OH} = -400 \mu A$                |

| I <sub>CC2</sub> (3)           | V <sub>CC</sub> Supply Current                |                       | 30                    | mA   |                                      |

| I <sub>PP2</sub> (3)           | V <sub>PP</sub> Supply Current (Program)      |                       | 50                    | mA   | CE = VIL                             |

| V <sub>ID</sub>                | A <sub>9</sub> Intelligent Identifier Voltage | 11.5                  | 12.5                  | ٧    |                                      |

| V <sub>PP</sub> (1)            | Programming Voltage                           | 12.5                  | 13.0                  | ٧    |                                      |

| V <sub>CC</sub> <sup>(1)</sup> | Supply Voltage During Programming             | 6.0                   | 6.5                   | V    |                                      |

#### **AC PROGRAMMING CHARACTERISTICS**

$T_A = 25^{\circ}C \pm 5^{\circ}C$ ; see Table 2 for  $V_{CC}$  and  $V_{PP}$  voltages.

| Symbol                          | Parameter                        |     | Conditions |     |      |            |

|---------------------------------|----------------------------------|-----|------------|-----|------|------------|

|                                 | i qiqilletel                     | Min | Тур        | Max | Unit | Oonditions |

| tas                             | Address Setup Time               | 2   |            |     | μs   |            |

| toes                            | OE Setup Time                    | 2   |            |     | μs   |            |

| t <sub>DS</sub>                 | Data Setup Time                  | 2   |            |     | μs   |            |

| t <sub>AH</sub>                 | Address Hold Time                | 0   |            |     | μs   |            |

| t <sub>DH</sub>                 | Data Hold Time                   | 2   |            |     | μs   |            |

| t <sub>DFP</sub> (2)            | OE High to<br>Output Float Delay | 0   |            | 130 | ns   |            |

| t <sub>VPS</sub> <sup>(1)</sup> | V <sub>PP</sub> Setup Time       | 2   |            |     | μs   |            |

| t <sub>VCS</sub> (1)            | V <sub>CC</sub> Setup Time       | 2   |            |     | μs   |            |

| tpw                             | CE Program Pulse Width           | 95  | 100        | 105 | μs   |            |

| t <sub>OE</sub>                 | Data Valid from OE               |     |            | 150 | ns   |            |

#### NOTES:

1.  $V_{CC}$  must be applied simultaneously or before  $V_{PP}$  and removed simultaneously or after  $V_{PP}$ .

3. The maximum current value is with outputs 00 to 07 unloaded.

<sup>2.</sup> This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven—see timing diagram.

1. The input timing reference level is  $V_{IL}=0.8V$  and  $V_{IH}=2V$ .

2. t<sub>OE</sub> and t<sub>DFP</sub> are device characteristics but must be accommodated by the programmer.

3. To prevent device damage during programming, a 0.1 μF capacitor is required between V<sub>PP</sub> and ground to suppress spurious voltage transients.

4. During programming, the address latch function is bypassed whenever V<sub>PP</sub> = 12.75V or A<sub>g</sub> = V<sub>H</sub>. When V<sub>PP</sub> and A<sub>g</sub> are at TTL levels, the address latch function is enabled, and the device functions in read mode.

5. Vpp can be 12.75V during Blank Check and Final Verify; if so, CE must be VIH.

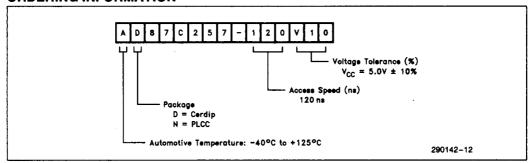

## **ORDERING INFORMATION**

Valid Combinations:

AD87C257-120V10 AN87C257-120V10 AD87C257-200V10 AN87C257-200V10

## **REVISION HISTORY**

| Number | Description                |

|--------|----------------------------|

| 004    | Added the 120 ns speed bin |