# 1024 X 4 N-MOS TTL IN/Out

#### **Features**

- 1024 words x 4 bits

- Three access times (200, 300, and 450 nSec)

- Low power device 175 mW typical

- Standard power device 225 mW typical

- Common output bus

- Three-state output drivers

- Fully STATIC no clock or refresh

- Single +5V power supply

- TTL compatible interface

- 18-pin ceramic, plastic or cerdip package

### **General Description**

GTE Series 2114 RAMs are 1024 word x 4 bit static N-MOS Random Access Memories. These fully static memory cells require no external clocks, strobes or data refresh circuitry. TTL compatible Three-State output drivers allow the use of common I/O linesideally suited for microprocessor interfacing to a common I/O bus. A single +5V input is the only power supply requirement. Read/Write functions are controlled by the low state of Chip Select (CS) and the concurrent high or low level of Write Enable (WE) to initiate a Read or Write cycle respectivelywith no pulse or edge triggering required. With CS high (STANDBY), a high impedance is reflected to the I/O bus - resulting in a no-load condition when nonselected. The 2114 is available in a choice of access times, power dissipation and packaging to meet your particular requirement.

#### **Truth Table** $\overline{cs}$ WE DI/DO STATUS MODE Н Don't High Deselect Standby Care L н Data Selected Read L L Selected Write L L Selected Write

| _ |    |     |     |     |    |

|---|----|-----|-----|-----|----|

| S | рe | cif | ica | tio | ns |

|         | Max Access<br>Time<br>(nSec) | Min Cycle<br>Time<br>(nSec) | Max. ICC<br>Supply<br>Current<br>(mA) | Typ. I <sub>CC</sub><br>Supply<br>Current<br>(mA) |

|---------|------------------------------|-----------------------------|---------------------------------------|---------------------------------------------------|

| 2114-2  | 200                          | 200                         | 100                                   | 50                                                |

| 2114-3  | 300                          | 300                         | 100                                   | 50                                                |

| 2114-U  | 450                          | 450                         | 100                                   | 45                                                |

| L2114-2 | 200                          | 200                         | 70                                    | 35                                                |

| L2114-3 | 300                          | 300                         | 70                                    | 35                                                |

| L2114-U | 450                          | 450                         | 70                                    | 35                                                |

**Microcircuits**

V ORIG

002560

T- 2560

# Recommended Operating Conditions (T<sub>AMB</sub> = 0° C to 70° C)

| Parameter        | Symbol          | Min  | Nom | Max  | Units |

|------------------|-----------------|------|-----|------|-------|

| Sup-ply Voltage  | v <sub>cc</sub> | 4.75 | 5.0 | 5.25 | V     |

| Input High Level | V <sub>IH</sub> | 2.0  | _   | 5.25 | V     |

| Input Low Level  | VIL             | -0.5 | _   | 0.8  | V     |

# DC Electrical Characteristics (Full Operating Voltage and Temperature Range)

| Characteristic        | Symbol          | Min | Тур | Max | Unit | Conditions                                 |

|-----------------------|-----------------|-----|-----|-----|------|--------------------------------------------|

| Input Leakage Current | <sup>1</sup> LI | -10 | _   | +10 | μΑ   | V <sub>IN</sub> = 0 to 5.25V               |

| I/O Leakage Current   | <sup>1</sup> LO | -10 | _   | +10 | μΑ   | V <sub>I/O</sub> = 0.4 to 5.25V, CS = 2.4V |

| Output Voltage High   | Voн             | 2.4 |     | _   | V    | I <sub>O</sub> = -1.0 mA                   |

| Output Voltage Low    | VOL             | -   | _   | 0.4 | V    | I <sub>O</sub> = 2.1 mA                    |

| Power Supply Current  |                 |     |     |     |      |                                            |

|                       | ¹cc             | _   | 50  | 70  | mA   | T <sub>AMB</sub> = 25°C                    |

| 2114-2,3              | lcc             | _   | -   | 100 | mA   | T <sub>AMB</sub> = 0°C to 70°C             |

| 1 0444 0 2            | ¹cc             | _   | 35  | 65  | mA   | T <sub>AMB</sub> = 25°C                    |

| L2114-2,3             | ¹cc             | -   | -   | 70  | mA   | T <sub>AMB</sub> = 0°C to 70°C             |

| 044411                | ¹cc             | _   | 45  | 75  | mA   | T <sub>AMB</sub> = 25°C                    |

| 2114-∪                | ¹cc             | _   | 65  | 100 | mA   | T <sub>AMB</sub> = 0°C to 70°C             |

| 1.044411              | ¹cc             | _   | 35  | 45  | mA   | T <sub>AMB</sub> = 25°C                    |

| L2114-U               | <sup>1</sup> CC | _   | 40  | 70  | mA   | T <sub>AMB</sub> = 0°C to 70°C             |

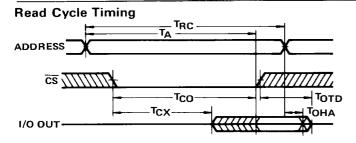

# Read Cycle — AC Characteristics (Full Operating Voltage and Temperature Range)

|                                       |                 | 2114-2, L2114-2 2114-3, L2 |     | L2114-3 | 2114-U, | L2114-U |     |      |

|---------------------------------------|-----------------|----------------------------|-----|---------|---------|---------|-----|------|

| Parameter                             | Symbol          | Min                        | Max | Min     | Max     | Min     | Max | Unit |

| Read Cycle Time                       | TRC             | 200                        | ~   | 300     | ∞       | 450     | ∞   | nS   |

| Access Time                           | TA              | -                          | 200 |         | 300     | _       | 450 | nS   |

| Chip Select-to-Output, Valid          | тсо             | _                          | 70  | _       | 100     |         | 120 | nS   |

| Chip Select-to-Output, Active         | T <sub>CX</sub> | 20                         |     | 20      | _       | 20      | -   | nS   |

| Output Hold After Address Change      | ТОНА            | 50                         | _   | 50      |         | 50      | -   | nS   |

| Output Disable After Chip Deselection | ТОТД            | _                          | 60  | _       | 80      | _       | 100 | nS   |

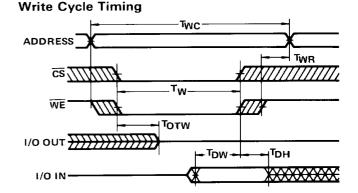

# Write Cycle — AC Characteristics (Full Operating Voltage and Temperature Range)

|                           |                  | 2114-2, L2114-2 |     | 2114-3, | 2114-3, L2114-3 |     | 2114-U, L2114-U |      |

|---------------------------|------------------|-----------------|-----|---------|-----------------|-----|-----------------|------|

| Parameter                 | Symbol           | Min             | Max | Min     | Max             | Min | Max             | Unit |

| Write Cycle Time          | T <sub>WC</sub>  | 200             | ∞   | 300     | ∞               | 450 | ∞               | nS   |

| Write Pulse Width         | T <sub>W</sub>   | 120             | _   | 150     | _               | 200 |                 | nS   |

| Write Recovery Time       | TWR              | 0               | _   | 0       | _               | 0   | -               | nS   |

| Data Setup Time           | T <sub>DW</sub>  | 120             | _   | 150     |                 | 200 | -               | nS   |

| Data Hold Time            | Трн              | 0               | _   | 0       | _               | 0   | _               | nS   |

| Output Disable From Write |                  |                 |     |         |                 |     |                 |      |

| or Chip Enable Time       | T <sub>OTW</sub> |                 | 60  | _       | 80              | _   | 100             | nS   |

## Capacitance

| Parameter          | Symbol           | Тур | Max | Unit | Conditions           |

|--------------------|------------------|-----|-----|------|----------------------|

| Input Capacitance  | c <sub>IN</sub>  | 4   | 5   | pF   | V <sub>IN</sub> = 0V |

| Output Capacitance | c <sub>I/O</sub> | 4   | 5   | pF   | V <sub>1/O</sub>     |

## Absolute Maximum Ratings (See Note 1) (Referenced to GND)

| _                                                          |              | -    |

|------------------------------------------------------------|--------------|------|

| RATING                                                     | VALUE        | UNIT |

| Voltage on Any Pin With<br>Respect to GND                  | -0.5 to +7.0 | Vdc  |

| Power Dissipation                                          | 1.0 (NOTE 2) | W    |

| Operating Ambient<br>Temperature Range (T <sub>AMB</sub> ) | 0 to +70     | °C   |

| Temperature Under<br>Bias (TBIAS)                          | -10 to +80   | °C   |

| Storage Temperature (TSTOR)                                | -65 to +150  | °C   |

| Current Into/From<br>Output (I <sub>O</sub> )              | 50           | mA   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated values.

NOTE 1:Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended or maximum voltages for extended periods of time could affect device reliability.

NOTE2:At 25°C Ambient. Derate 13.5 mW/°C.

#### NOTES:

- 1. WE is high for a Read Cycle.

- 2. Tw is measured from the latter of CS or WE going low to the earlier of CS or WE going high.

- WE or CS must be high prior to a write cycle to prevent an erroneous write during the address transitions.

## **Functional Description**

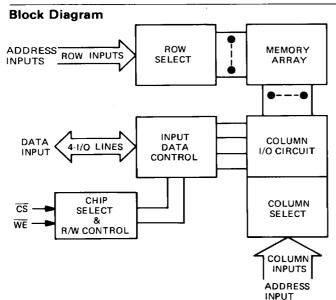

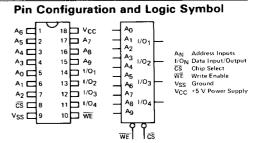

The GTE Microcircuits 2114 is a 4096 bit static RAM, organized in a 1024 word by 4 bit configuration. Each word is selectively accessed by address lines Ao through Ag, with data being read or written on common data input/output lines (I/O<sub>1</sub> through I/O<sub>4</sub>), as controlled by the Chip Select (CS) and Write Enable (WE) functions.

Since no address setup time is required, data access is quite simple. With  $\overline{WE}$  high and  $\overline{CS}$  low, the array may be read by simply toggling the input address. Valid data output becomes available after time TA, following each address change. However, should  $\overline{CS}$  be used to control the read mode, valid data access time must be equal to or greater than TA, but cannot occur earlier than TCO from  $\overline{CS}$  going low.

The write mode is enabled whenever  $\overline{CS}$  and  $\overline{WE}$  are both low. Stored data integrity is therefore preserved as long as either  $\overline{CS}$  or  $\overline{WE}$  is high. To write valid data, the address input

may be applied simultaneously with the write enable (CS and WE both low), but must remain stable for the period TWC while writing.

Possible write modes are as follows:

- CS is held low. T<sub>W</sub> is then defined by WE going from a high state to a low state and T<sub>WR</sub> is defined by WE going from a low state to a high state.

- WE is held low. CS going low is then used to define Tw..

GS going high is used to define Twn.

- 3.  $\overline{CS}$  and  $\overline{WE}$  are both used. Tw timing is defined by the latter of  $\overline{CS}$  or  $\overline{WE}$  going low, and Twp timing is determined by the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high.

The address must remain stable for the full Write cycle. However, data inputs are not required to remain stable for the full cycle. The correct logic level will be entered as long as input data is stable for the time period T<sub>DW</sub> during the write cycle.

#### **Functional Notes:**

- 1.  $T_{AW}$  is measured from the latter of  $\overline{CS}$  or  $\overline{WE}$  going low.

- 2. Tw is measured from the latter of  $\overline{CS}$  or  $\overline{WE}$  going low, to the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high.

- 3. TWR is measured from the earlier of  $\overline{CS}$  or  $\overline{WE}$  going high.

- TDH and TDW are measured from the earlier of CS or WE going high.

- TOTW is measured from WE going low or CS going high, whichever occurs first.

- 6. Timing diagrams are based on loading to simulate the capacitive effect of twenty (20) additional outputs

- connected in parallel (100 pF) plus the current loading affect of one TTL input load.

- 7. Input pulse levels are 0.8 volts for logic low, to 2.0 volts for logic high.

- 8. Input rise and fall times are of equal value (10 nS).

- 9. Timing is measured from the 1.5 volt level whether the level is going high or low.

- Each I/O line is a high impedance during the write mode, or when CS is high. Inputs always represent a high impedance.

# GTE 2114 Static RAMs 1024 x 4 N-MOS TTL In/Out

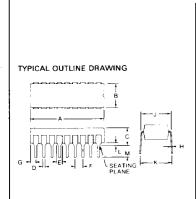

# **Packaging Dimensions**

| "B" PLASTIC PACKAGE |        |        |       |       |  |  |  |  |

|---------------------|--------|--------|-------|-------|--|--|--|--|

| ым                  | MILLIM | ETERS  | INC   | CHES  |  |  |  |  |

| ווווט               | MIN    | MAX    | MIN   | MAX   |  |  |  |  |

| Α                   | 21.590 | 23.622 | 0.850 | 0.930 |  |  |  |  |

| В                   | 6.096  | 7.493  | 0.240 | 0.295 |  |  |  |  |

| С                   |        | 5.588  | -     | 0.210 |  |  |  |  |

| D                   | 0.381  | 0.584  | 0.015 | 0.023 |  |  |  |  |

| E                   | 1.143  | 1.778  | 0.045 | 0.070 |  |  |  |  |

| F                   | 2.286  | 2.794  | 0.090 | 0.110 |  |  |  |  |

| G                   | 0.635  | 2.159  | 0.025 | 0.085 |  |  |  |  |

| H                   | 0.203  | 0.305  | 0.008 | 0.012 |  |  |  |  |

| J                   | 7.366  | 8.255  | 0.290 | 0.325 |  |  |  |  |

| К                   | 7.366  | 10.414 | 0.290 | 0.410 |  |  |  |  |

| L                   | 0.508  | 1.278  | 0.020 | 0.050 |  |  |  |  |

| M                   | 2.540  | 4.191  | 0.100 | 0.165 |  |  |  |  |

|     | "A" CERAMIC PACKAGE |        |        |       |  |  |  |  |

|-----|---------------------|--------|--------|-------|--|--|--|--|

| DIM | MILLIM              | ETERS  | INCHES |       |  |  |  |  |

| DIN | MIN                 | MAX    | MIN    | MAX   |  |  |  |  |

| А   | 22.606              | 23.114 | 0.890  | 0.910 |  |  |  |  |

| В   | 7.061               | 7.569  | 0.278  | 0.298 |  |  |  |  |

| С   | _                   | 4.826  | _      | 0.190 |  |  |  |  |

| D   | 0.381               | 0.584  | 0.015  | 0.023 |  |  |  |  |

| Е   | 1.016               | 1.778  | 0.040  | 0.070 |  |  |  |  |

| F   | 2.286               | 2.794  | 0.090  | 0.110 |  |  |  |  |

| G   | 0.762               | 1.778  | 0.030  | 0.070 |  |  |  |  |

| Н   | 0.203               | 0.305  | 0.008  | 0.012 |  |  |  |  |

| J   | 7.620               | 8.077  | 0.300  | 0.318 |  |  |  |  |

| K   | 7.62                | O REF  | 0.300  | REF   |  |  |  |  |

| L   | 0.635               | 1.651  | 0.025  | 0.065 |  |  |  |  |

| М   | 2.540               | 3.810  | 0.100  | 0.150 |  |  |  |  |

| "E" CERDIP PACKAGE |        |        |       |       |  |  |  |

|--------------------|--------|--------|-------|-------|--|--|--|

| DIM                | MILLIM | ETERS  | INC   | CHES  |  |  |  |

| DIN                | MIN    | MAX    | MIN   | MAX   |  |  |  |

| Α                  | 22.402 | 23.495 | 0.882 | 0.925 |  |  |  |

| В                  |        | 7.874  |       | 0.310 |  |  |  |

| С                  |        | 4.826  | _     | 0.190 |  |  |  |

| D                  | 0.381  | 0.584  | 0.015 | 0.023 |  |  |  |

| E                  | 1.143  | 1.651  | 0.045 | 0.065 |  |  |  |

| F                  | 2.286  | 2.794  | 0.090 | 0.110 |  |  |  |

| G                  | 0.381  | 1.270  | 0.015 | 0.050 |  |  |  |

| Н                  | 0.203  | 0.305  | 0.008 | 0.012 |  |  |  |

| J                  | 7.366  | 8.128  | 0.290 | 0.320 |  |  |  |

| ĸ                  | 8.255  | 9.906  | 0.325 | 0.390 |  |  |  |

| L                  | 0.381  | 1.016  | 0.015 | 0.040 |  |  |  |

| М                  | 2.540  | 3.937  | 0.100 | 0.155 |  |  |  |

### **Ordering Information**

| DEVICE    | ACCESS<br>TIME | MAXIMUM<br>POWER<br>DISSIPATION | PACKAGE        | TEMP. RANGE |

|-----------|----------------|---------------------------------|----------------|-------------|

| 2114-2CA  | 200 nS         | 525 mW                          | 18-pin Ceramic | 0°C to 70°C |

| 2114-2CB  | 200 nS         | 525 mW                          | 18-pin Plastic | 0°C to 70°C |

| 2114-2CE  | 200 nS         | 525 mW                          | 18-pin Cerdip  | 0°C to 70°C |

| L2114-2CA | 200 nS         | 368 mW                          | 18-pin Ceramic | 0°C to 70°C |

| L2114-2CB | 200 nS         | 368 mW                          | 18-pin Plastic | 0°C to 70°C |

| L2114-2CE | 200 nS         | 368 mW                          | 18-pin Cerdip  | 0°C to 70°C |

| 2114-3CA  | 300 nS         | 525 mW                          | 18-pin Ceramic | 0°C to 70°C |

| 2114-3CB  | 300 nS         | 525 mW                          | 18-pin Plastic | 0°C to 70°C |

| 2114-3CE  | 300 nS         | 525 mW                          | 18-pin Cerdip  | 0°C to 70°C |

| L2114-3CA | 300 nS         | 368 mW                          | 18-pin Ceramic | 0°C to 70°C |

| L2114-3CB | 300 nS         | 368 mW                          | 18-pin Plastic | 0°C to 70°C |

| L2114-3CE | 300 nS         | 368 mW                          | 18-pin Cerdip  | 0°C to 70°C |

| 2114-UCA  | 450 nS         | 525 mW                          | 18-pin Ceramic | 0°C to 70°C |

| 2114-UCB  | 450 nS         | 525 mW                          | 18-pin Plastic | 0°C to 70°C |

| 2114-UCE  | 450 nS         | 525 mW                          | 18-pin Cerdip  | 0°C to 70°C |

| L2114-UCA | 450 nS         | 315 mW                          | 18-pin Ceramic | 0°C to 70°C |

| L2114-UCB | 450 nS         | 315 mW                          | 18-pin Plastic | 0°C to 70°C |

| L2114-UCE | 450 nS         | 315 mW                          | 18-pin Cerdip  | 0°C to 70°C |

### WARNING:

MOS CIRCUITS ARE SUBJECT TO DAMAGE FROM STATIC DISCHARGE

Internal static discharge circuits are provided to minimize part damage due to environmental static electrical charge build-ups Industry established recommendations for handling MOS circuits include:

- Ship and store product in conductive shipping tubes or in conductive foam plastic. Never ship or store product in non-conductive plastic containers or non-conductive plastic foam material.

- 2. Handle MOS parts only at conductive work stations

- 3. Ground all assembly and repair tools

Represented in your area by:

GTE Microcircuits products are stocked at more than 70 distributor locations throughout the U.S. For the name of your nearest distributor, call Toll Free 800-526-6050, Ext. 1344

"The information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information, but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any GTE Microcircuits product is subject to all GTE Microcircuits Terms and Conditions of Sale and Sales Policies, copies of which are available upon request."

GTE Microcircuits/2000 West 14th Street/Tempe, Arizona 85281/(602)968-4431/TWX 910-951-1383

Reprinted April 1980

4

Published in U.S.A.